Page 37 - husk_nvidia_-2_n13p-gl

P. 37

D C B A

9 -2 -2 -2

9 14,15 Rev Rev Rev 103 103 103

M_VREF_DQ_DIMM0_C 20 M_VREF_DQ_DIMM1_C 20 DDR3_DRAMRST# Wistron Corporation Wistron Corporation Wistron Corporation of of of

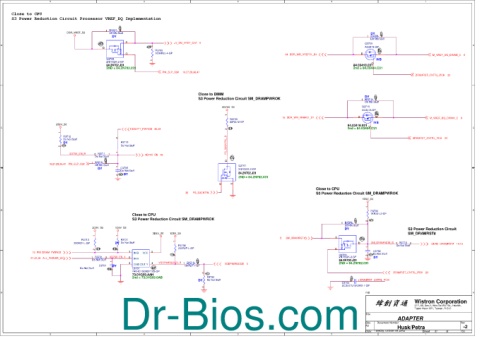

DRAMRST_CNTRL_PCH S3 Power Reduction Circuit 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Taipei Hsien 221, Taiwan, R.O.C. Taipei Hsien 221, Taiwan, R.O.C. 37 37 37

1 DRAMRST_CNTRL_PCH SM_DRAMRST# 20 Sheet Sheet Sheet 1

R3718 R3718 1 Do Not Stuff 2 Do Not Stuff DRAMRST_CNTRL_PCH ADAPTER ADAPTER ADAPTER Husk/Petra Husk/Petra Husk/Petra

2 Do Not Stuff Do Not Stuff S IVB IVB 1KR2J-L2-GP 1KR2J-L2-GP SM_DRAMRST#_D Do Not Stuff Do Not Stuff Document Number Document Number Document Number Tuesday, October 09, 2012 Tuesday, October 09, 2012 Tuesday, October 09, 2012

DY DY R3708 R3708 AO3418-GP AO3418-GP 2 Do Not Stuff Do Not Stuff S IVB IVB R3706 R3706 C3702 C3702 DY DY DRAMRST_CNTRL_PCH

1 Q3709 Q3709 2nd = 84.03404.C31 2nd = 84.03404.C31 DY DY R3714 R3714 Q3710 Q3710 AO3418-GP AO3418-GP G 1D5V_S3 1 2 1 2 IVB IVB IVB Title Title Title Size Size Size A3 A3 A3 Date: Date: Date:

D 84.03418.031 84.03418.031 G 1 D 84.03418.031 84.03418.031 2nd = 84.03404.C31 2nd = 84.03404.C31 S3 Power Reduction Circuit SM_DRAMPWROK R3709 R3709 2 Do Not Stuff Do Not Stuff DY DY D 2N7002K-2-GP 2N7002K-2-GP 84.2N702.J31 84.2N702.J31 2ND = 84.2N702.031 2ND = 84.2N702.031 1 C3703 2 SCD047U16V2KX-1-GP SCD047U16V2KX-1-GP

Close to CPU

2 1 S G Q3703 Q3703 C3703 2

DDR_WR_VREF01_B4 DDR_WR_VREF01_D1 SM_DRAMRST#

14

15

5

S3 Power Reduction Circuit SM_DRAMPWROK Q3701 Q3701 2N7002K-2-GP 2N7002K-2-GP 84.2N702.J31 84.2N702.J31 2ND = 84.2N702.031 2ND = 84.2N702.031 5 Dr-Bios.com

3 0D75V_S0 1 R3703 R3703 22R2J-2-GP 22R2J-2-GP 2 PS_S3CNTRL_D D S VDDPWRGOOD 3

Close to DIMM G R3720 R3720 Do Not Stuff Do Not Stuff

9 PS_S3CNTRL 2 2 DY DY 1

+V_SM_VREF_CNT 19,27,29,36,47 36 1D5V_S0 R3702 R3702 200R2F-L-GP 200R2F-L-GP R3719 R3719 1 130R2F-1-GP 130R2F-1-GP

100KR2J-4-GP 100KR2J-4-GP PM_SLP_S3# 46 S3 Power Reduction Circuit SM_DRAMPWROK 1 2 VDDPWRGOOD_R

R3705 R3705 45,48 3D3V_S5 5 4

S3 Power Reduction Circuit Processor VREF_DQ Implementation

1D05VTT_PWRGD IN B IN A GND OUT Y U3701 U3701

4 2 1 0D75V_EN Close to CPU VCC 74VHC1G09DFT2G-GP 74VHC1G09DFT2G-GP 73.01G09.AAH 73.01G09.AAH 2nd = 73.01G09.0AB 2nd = 73.01G09.0AB 4

S G R3710 R3710 Do Not Stuff Do Not Stuff C3705 C3705 Do Not Stuff Do Not Stuff DY DY R3721 R3721 Do Not Stuff Do Not Stuff 1 2 3

2 2ND = 84.2N702.031 2ND = 84.2N702.031 1D5V_S3 0D75V_EN_1

R3707 R3707 Do Not Stuff Do Not Stuff DY DY Q3708 Q3708 2N7002K-2-GP 2N7002K-2-GP 84.2N702.J31 84.2N702.J31 2 1 1 2 1 DY DY 2 1 DY DY 2

1 2

R3711 R3711 Do Not Stuff 1 Do Not Stuff R3716 R3716 Do Not Stuff Do Not Stuff DY DY R3701 R3701 Do Not Stuff 2 Do Not Stuff

D C3701 C3701

2 3D3V_S5 1 2

1 R3713 R3713 1 Do Not Stuff Do Not Stuff

DDR_VREF_S3 Do Not Stuff Do Not Stuff 0D75V_EN_R PM_SLP_S3# 200R2F-L-GP 200R2F-L-GP

3D3V_S0 1 R3712 R3712 DY DY 2 19,27,29,36,47

5 PM_DRAM_PWRGD ALL_POWER_OK 5

Close to CPU 19 27,42,48

D C B A