Page 99 - husk_nvidia_-2_n13p-gl

P. 99

D C B A Rev Rev Rev -2 103 -2 103 -2 103

Wistron Corporation Wistron Corporation Wistron Corporation 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, Taipei Hsien 221, Taiwan, R.O.C. Taipei Hsien 221, Taiwan, R.O.C. Taipei Hsien 221, Taiwan, R.O.C. of of of 99 99 99 Sheet Sheet Sheet

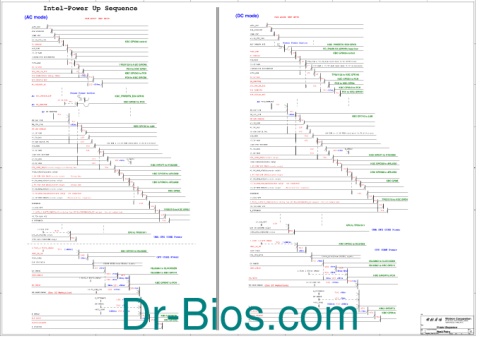

Document Number Power Sequence Document Number Power Sequence Document Number Power Sequence Husk/Petra Husk/Petra Husk/Petra

1 Thursday, April 19, 2012 Thursday, April 19, 2012 Thursday, April 19, 2012 1

IVB IVB IVB Title Title Title Size Size Size A1 A1 A1 Date: Date: Date:

KBC GPIO71 to RT8208B KBC GPIO30 to APL5930 KBC GPIO66 to APL5930 KBC GPI95 T33 T35 TPS51218 to KBC GPI34 T36 T37 T38 UMA GFX CORE Power CPU CORE Power ISL62883 to CLOCKGEN ISL62884 to KBC GPO14 KBC GPIO47 to PCH KBC LRESET# T53 >1ms T54 KBC GPIO45 T55

KBC GPO16 to LAN

KBC_PWRBTN_EC# GPIO3 EC_ENABLE# (GPIO51) keep low KBC GPIO36 control TPS51125 to KBC GPIO46 KBC GPO84 to PCH PCH to KBC GPI94 KBC GPIO43 to PCH PCH to KBC GPIO01 T13 +5V_RUN & +3.3V_RUN need meet 0.7V difference H_PWRGD T25 >1ms T28 T29 T30 T31 T32 T34 CPU to TPS51611 KBC GPO53 to ISL62883 T45 Delay 10ms T48 >1ms >1ms >1ms 0.05ms< <650ms T52

2 +5V_ALW & +3.3V_ALW need meet 0.7V difference +5V_ALW & +3.3V_ALW need meet 0.7V difference T9 T10 T11 T12 >10ms T22 T23 T24 T26 T27 CLKIN_BCLK(from CK505) stable >1ms 43 >1ms T44 >5ms T46 3ms< T47 <20ms >100ns T49 +1.5V_RUN_CPU H_VTTPWRGD T50 PM_PWROK T51 +VCC_CORE 2

red word: KBC GPIO Press Power button T3 T4 T5 T6 T7 T8 T15 >30us T16 T17 T18 T19 T20 T21 -->Reserved for sequence 1.5CPU_1.05VTT_PWRGD(after delay 1ms GPI96-VDDPWRGOOD_EC output for s3 reduction) T40 ( >99ms ) T42 <3ms 1.5CPU_1.05VTT_PWRGD

T1 T2 +5VALW_PCH_VCC5REFSUS PCH_RSMRST# DC T14 +V_DDR_REF(0.9V) +5VS_PCH_VCC5REF GFX_CORE_EN(Discrete only) +VGA_CORE(Discrete only) 1.0V_RUN_VGA_EN(Discrete only) +1.0V_RUN_VGA(Discrete only) 1.8V_VGA_RUN_EN(Discrete only) +1.8V_RUN_VGA(Discrete only) +3.3V_RUN_VGA_EN(Discrete only)-->DY reserved +3.3V_RUN_VGA(Discrete only) +1.05V_VTT T39 GFX_VR_EN(UMA only) +CPU_GFX_CORE(UMA only) 1.5CPU_1.05VTT_PWRGD T41 (for S3 Reduction)

(DC mode) +RTC_VCC PCH_RTCRST# +PWR_SRC +3.3V_RTC_LDO KBC_PWRBTN_EC# +KBC_PWR S5_ENABLE +5V_ALW +3.3V_ALW +15V_ALW 3V_5V_POK PM_PWRBTN# SUS_PWR_DN_ACK PCH_RSMRST# PCH_SUSCLK_KBC PM_SLP_S4# PM_SLP_S3# PM_LAN_ENABLE +3.3V_LAN +1.5V_SUS +5V_RUN +3.3V_RUN +1.5V_RUN +1.8V_RUN RUNPWROK +1.05V_VTT +0.75V_DDR_VTT H_VTTPWRGD IMVP_VR_ON +VCC_CORE CLK_CPU_BCLK CK_PWRGD IMVP_PWRGD PM_PWROK PM_DRAM_PWRGD H_PWRGD PLT_RST# PLTRST_DELAY# H_CP

3 >100ns Dr-Bios.com 3

KBC GPIO71 to RT8208B KBC GPIO30 to APL5930 KBC GPIO66 to APL5930 KBC GPI95 TPS51218 to KBC GPI34 T36 T37 T38 UMA GFX CORE Power CPU CORE Power ISL62883 to CLOCKGEN ISL62884 to KBC GPO14 KBC GPIO47 to PCH KBC LRESET# KBC GPIO45 T55

4 KBC GPIO36 control TPS51125 to KBC GPIO46 PCH to KBC GPI94 KBC GPIO43 to PCH PCH to KBC GPIO00 KBC_PWRBTN_EC# GPIO3 KBC GPO84 to PCH KBC GPO16 to LAN +5V_RUN & +3.3V_RUN need meet 0.7V difference H_PWRGD T25 >1ms T28 T29 T30 T31 T32 T33 T34 T35 CPU to TPS51611 KBC GPO53 to ISL62883 CLKIN_BCLK(from CK505) stable T45 Delay 10ms T47 <20ms T48 >1ms >1ms T50 >1ms T51 0.05ms< <650ms T52 T53 >1ms T54 4

Intel-Power Up Sequence red word: KBC GPIO T6 T8 T9 T10 >10ms T11 <200ms T12 Press Power button T13 T15 >30us T16 T17 T18 T19 T20 T21 T22 T23 T24 T26 T27 -->Reserved for sequence 1.5CPU_1.05VTT_PWRGD(after delay 1ms GPI96-VDDPWRGOOD_EC output for s3 reduction) T40 T42 <3ms >1ms 43 >1ms T44 1.5CPU_1.05VTT_PWRGD >5ms T46 3ms< +1.5V_RUN_CPU T49 H_VTTPWRGD PM_PWROK +VCC_CORE

5 T1 T2 T3 T4 T5 +5VALW_PCH_VCC5REFSUS T7 PCH_RSMRST#(EC Delay 40ms) KBC_PWRBTN_EC# 3V_5V_POK PM_PWRBTN# AC T14 GFX_CORE_EN(Discrete only)------Delay 5ms +VGA_CORE(Discrete only) 1.0V_RUN_VGA_EN(Discrete only)------Delay 4ms +1.0V_RUN_VGA(Discrete only) 1.8V_VGA_RUN_EN(Discrete only)------Delay 5ms +1.8V_RUN_VGA(Discrete only) +3.3V_RUN_VGA_EN(Discrete only)-->DY reserved +3.3V_RUN_VGA(Discrete only) +1.05V_VTT T39 +CPU_GFX_CORE(UMA only) 1.5CPU

(AC mode) +RTC_VCC PCH_RTCRST# +PWR_SRC +3.3V_RTC_LDO S5_ENABLE +5V_ALW +3.3V_ALW +15V_ALW 3V_5V_POK SUS_PWR_DN_ACK PCH_SUSCLK_KBC AC_PRESENT_EC AC PM_PWRBTN# AC PM_SLP_S4# PM_SLP_S3# PM_LAN_ENABLE +3.3V_LAN +1.5V_SUS +V_DDR_REF(0.9V) +5V_RUN +3.3V_RUN +5VS_PCH_VCC5REF +1.5V_RUN +1.8V_RUN RUNPWROK +1.05V_VTT +0.75V_DDR_VTT H_VTTPWRGD GFX_VR_EN(UMA only) IMVP_VR_ON +VCC_CORE CLK_CPU_BCLK CK_PWRGD IMVP_PWRGD PM_PWROK PM_DRAM_PWR

D C B A