Page 2 - husk_nvidia_-2_n13p-gl

P. 2

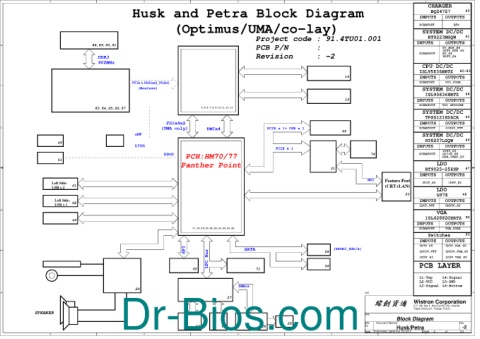

D C B A

40 41 42~43 44 45 46 47 48 92 93 Rev Rev Rev -2 -2 -2 103 103 103

OUTPUTS BT+ OUTPUTS 5V_AUX_S5 3D3V_AUX_S5 3D3V_S5 OUTPUTS VCC_CORE OUTPUTS VCC_GFXCORE OUTPUTS 1D05V_VTT OUTPUTS 1D5V_S3 0D75V_S0 DDR_VREF_S3 OUTPUTS 1D8V_S0 OUTPUTS 0D85V_S0 OUTPUTS VGA_CORE OUTPUTS 3D3V_VGA_S0 1D05V_VGA_S0 1D5V_VGA_S0 L4:Signal L5:GND L6:Bottom

CHARGER BQ24727 SYSTEM DC/DC RT8223MGQW 5V_S5 CPU DC/DC ISL95836HRTZ SYSTEM DC/DC ISL95836HRTZ SYSTEM DC/DC TPS51218DSCR SYSTEM DC/DC RT8207LGQW LDO RT9025-25ZSP LDO G978 VGA ISL62882CHRTZ Switches PCB LAYER Wistron Corporation Wistron Corporation Wistron Corporation 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih, of of of 2 2 2

1 INPUTS DCBATOUT INPUTS DCBATOUT INPUTS DCBATOUT INPUTS DCBATOUT INPUTS DCBATOUT INPUTS DCBATOUT 26 INPUTS 3D3V_S0 INPUTS 1D05_VTT INPUTS DCBATOUT INPUTS 3D3V_S0 26 1D05V_VTT 1D5V_S3 L1:Top L2:VCC L3:Signal Taipei Hsien 221, Taiwan, R.O.C. Taipei Hsien 221, Taiwan, R.O.C. Taipei Hsien 221, Taiwan, R.O.C. Block Diagram Block Diagram Block Diagram Sheet Sheet Sheet 1

Feature Port (CRT+LAN) 50 Document Number Document Number Document Number Husk/Petra Husk/Petra Husk/Petra Wednesday, September 05, 2012 Wednesday, September 05, 2012 Wednesday, September 05, 2012

74 MDI

SD/MMC IVB IVB IVB Title Title Title Size Size Size A3 A3 A3 Date: Date: Date:

Slot 0 14 Slot 1 15 65 (SATA3_6Gb/s)

2 Project code : 91.4TU01.001 DDRIII 1600/1333 DDRIII 1600/1333 Mini-Card and BT 802.11a/b/g LAN RTL8411 31 HDD 56 ODD 56 2

PCB P/N : Revision : -2 DDRIII 1333/1600 Channel A DDRIII 1333/1600 Channel A PCIE x 1+ USB x 1 PCIE x 1 RGB Fan 28

3 Husk and Petra Block Diagram (Optimus/UMA/co-lay) SATA LPC debug port 71 SMBus 27 Thermal NCT 7718W 28 69 25 Dr-Bios.com 3

Intel CPU 17W/GT2 Ivy Bridge Sandy Bridge 4,5,6,7,8,9,10,11,12,13 DMIx4 Intel PCH:HM70/77 Panther Point 4 USB 3.0 / 14 USB 2.0/1.1 ports ETHERNET (10/100/1000Mb) High Definition Audio SATA ports (6) PCIE ports (8) LPC I/F ACPI 1.1 17,18,19,20,21,22,23,24,25,26 LPC Bus 60 KBC NPCE885 Int. Touch KB 69

FDIx4x2 (UMA only) HDMI SPI Flash ROM 8MB PAD

PCIe x 16(Gen2_5Gb/s) AZALIA

4 (Muxless) eDP LVDS USB2.0 x 1 29 4

88,89,90,91 DDR3 900MHz 83.84,85,86,87 co-lay USB2.0 x 2 (USB2.0 + USB3.0) Azalia CODEC ALC271X

Nvidia N13P-GL 61 62 49

VRAM 1GByte 16 lane/128bit/29x29mm

LCD HDMI SPEAKER

5 49 51 Left Side: USB x 2 Left Side: USB x 1 CAMERA Internal Analog MIC 5

COMBO

D C B A