Page 98 - Digital Electronics by harish

P. 98

3.2.6 Ring counter

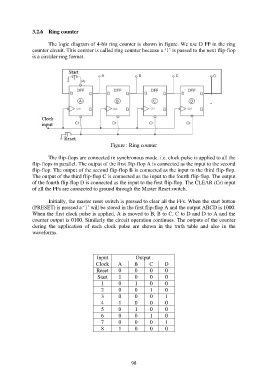

The logic diagram of 4-bit ring counter is shown in figure. We use D FF in the ring

counter circuit. This counter is called ring counter because a „1‟ is passed to the next flip-flop

is a circular ring format.

Figure : Ring counter

The flip-flops are connected in synchronous mode. i.e. clock pulse is applied to all the

flip-flops in parallel. The output of the first flip-flop A is connected as the input to the second

flip-flop. The output of the second flip-flop B is connected as the input to the third flip-flop.

The output of the third flip-flop C is connected as the input to the fourth flip-flop. The output

of the fourth flip-flop D is connected as the input to the first flip-flop. The CLEAR (Cr) input

of all the FFs are connected to ground through the Master Reset switch.

Initially, the master reset switch is pressed to clear all the FFs. When the start button

(PRESET) is pressed a „1‟ will be stored in the first flip-flop A and the output ABCD is 1000.

When the first clock pulse is applied, A is moved to B, B to C, C to D and D to A and the

counter output is 0100. Similarly the circuit operation continues. The outputs of the counter

during the application of each clock pulse are shown in the truth table and also in the

waveforms.

Input Output

Clock A B C D

Reset 0 0 0 0

Start 1 0 0 0

1 0 1 0 0

2 0 0 1 0

3 0 0 0 1

4 1 0 0 0

5 0 1 0 0

6 0 0 1 0

7 0 0 0 1

8 1 0 0 0

98